US008607086B2

### (12) United States Patent

#### Cullimore

### (10) **Patent No.:**

US 8,607,086 B2

(45) **Date of Patent:**

\*Dec. 10, 2013

# (54) MASSIVELY MULTICORE PROCESSOR AND OPERATING SYSTEM TO MANAGE STRANDS IN HARDWARE

(75) Inventor: Ian Henry Stuart Cullimore,

Leominster (GB)

(73) Assignee: IOTA Computing, Inc., Palo Alto, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 13/333,802

(22) Filed: Dec. 21, 2011

#### (65) **Prior Publication Data**

US 2013/0061078 A1 Mar. 7, 2013

#### Related U.S. Application Data

- (63) Continuation of application No. 13/224,938, filed on Sep. 2, 2011.

- (51) Int. Cl.

G06F 1/00 (2006.01)

G06F 1/26 (2006.01)

G06F 1/32 (2006.01)

G06F 15/16 (2006.01)

G06F 9/46 (2006.01)

- (52) **U.S. CI.**USPC ....... **713/323**; 713/300; 713/320; 709/201;

#### (58) Field of Classification Search

None

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,469,553 | Α           | 11/1995 | Patrick          |  |

|-----------|-------------|---------|------------------|--|

| 5,493,689 | A           | 2/1996  | Waclawsky et al. |  |

| 5,710,910 | A           | 1/1998  | Kehl et al.      |  |

| 5,896,499 | A           | 4/1999  | McKelvey         |  |

| 5,968,133 | A           | 10/1999 | Latham et al.    |  |

| 6,714,536 | В1          | 3/2004  | Dowling          |  |

| 7,002,979 | B1          | 2/2006  | Schneider et al. |  |

| 7,036,064 | В1          | 4/2006  | Kebichi et al.   |  |

|           | (Continued) |         |                  |  |

#### FOREIGN PATENT DOCUMENTS

| CN | 1622517      | 6/2005       |

|----|--------------|--------------|

| ΓW | 200924424    | 6/2009       |

| WO | WO2011056808 | 5/2011       |

|    | OTHER I      | PUBLICATIONS |

Ashkenazi et al. "Platform Independent Overall Security Architecture in Multi-Processor System-On-Chip ICs for Use in Mobile Phones and Handheld Devices," World Automation Congress, Jul. 24-26, 2006. [Accessed Feb. 18, 2011-Engineering Village].

#### (Continued)

Primary Examiner — Ji H Bae (74) Attorney, Agent, or Firm — Carr & Ferrell LLP

#### (57) ABSTRACT

A computing apparatus and corresponding method for operating are disclosed. The computing apparatus may comprise a set of interconnected central processing units (CPUs). Each CPU may embed an operating system including a kernel comprising a protocol stack. At least one of the CPUs may further embed executable instructions for allocating multiple strands among the rest of the CPUs. The protocol stack may comprise a Transmission Control Protocol/Internet Protocol (TCP/IP), a User Datagram Protocol/Internet Protocol (UDP/IP) stack, an Internet Control Message Protocol (ICMP) stack or any other suitable Internet protocol. The method for operating the computing apparatus may comprise receiving input/output (I/O) requests, generating multiple strands according to the I/O requests, and allocating the multiple strands to one or more CPUs.

#### 24 Claims, 6 Drawing Sheets

718/105

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 7,246,272 B2 7/2007 Cabezas et al. 7,308,686 B1 12/2007 Fotland et al. 7,334,124 B2 2/2008 Pham et al. 7,509,673 B2 3/2009 Swander et al. 7,657,933 B2 2/2010 Hussain et al. 7,694,158 B2* 4/2010 Melpignano et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7,055,173    | B1   | 5/2006  | Chaganty et al.           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|---------|---------------------------|

| 7,334,124 B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7,246,272    | B2   | 7/2007  |                           |

| 7,509,673 B2 3/2009 Swander et al. 7,657,933 B2 4/2010 Hussain et al. 7,694,158 B2* 4/2010 Melpignano et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7,308,686    | B1   | 12/2007 | Fotland et al.            |

| 7,657,933 B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7,334,124    | B2   | 2/2008  | Pham et al.               |

| 7,694,158 B2 * 4/2010 Melpignano et al                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7,509,673    | B2   | 3/2009  | Swander et al.            |

| 7,734,933 B1 6/2010 Marek et al. 7,770,179 B1 8/2010 James-Roxby et al. 7,886,340 B2 2/2011 Carley 8,055,822 B2 * 11/2011 Bernstein et al. 710/65 8,132,001 B1 3/2012 Patten et al. 709/235 2002/0007420 A1 * 1/2002 Eydelman et al. 709/235 2002/0167965 A1 * 11/2002 Beasley et al. 370/465 2003/0084190 A1 5/2003 Kimball 2004/0049624 A1 3/2004 Salmonsen 2004/0049624 A1 3/2004 Peikari 2004/0210320 A1 10/2004 Peikari 2004/0210320 A1 10/2004 Pandya 2006/0026162 A1 2/2006 Salmonsen et al. 2006/0133370 A1 6/2006 Eldar 2007/0008976 A1 1/2007 Meenan 2007/0022421 A1 1/2007 Meenan 2007/0118596 A1 5/2007 Patiejunas 709/203 2007/0211633 A1 9/2007 Gunawardena et al. 370/232 2007/0255861 A1 11/2007 Kain et al. 2008/0046891 A1 2/2008 Sanchorawala et al. 370/232 2009/0126003 A1 5/2009 Touboul 2009/0158299 A1 6/2009 Carter 719/319 2009/0235263 A1 9/2009 Furukawa 718/102 2010/00151716 A1 5/2010 Kuroda et al. 713/300 2010/0115716 A1 5/2010 Kuroda et al. 713/300 2010/0115719 A1 7/2010 Howard 709/201 2010/0185719 A1 7/2010 Ma et al. 2011/0002184 A1 1/2011 Kim 2011/0088037 A1 4/2011 Glistvain 2011/0107357 A1 5/2011 Cullimore 2012/0017262 A1 1/2012 Kapoor et al.                                                                                                             | 7,657,933    | B2   | 2/2010  | Hussain et al.            |

| 7,770,179 B1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7,694,158    | B2 * | 4/2010  | Melpignano et al 713/300  |

| 7,886,340 B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7,734,933    | В1   | 6/2010  | Marek et al.              |

| 8,055,822       B2 * 11/2011       Bernstein et al.       710/65         8,132,001       B1       3/2012       Patten et al.       709/235         2002/0007420       A1 * 1/2002       Eydelman et al.       709/235         2002/0167965       A1 * 11/2002       Beasley et al.       370/465         2003/0084190       A1       5/2003       Kimball         2004/0049624       A1       3/2004       Salmonsen         2004/0210320       A1       7/2004       Peikari         2004/0210320       A1       10/2004       Pandya         2006/0026162       A1       2/2006       Salmonsen et al.         2006/0133370       A1       6/2006       Eldar         2007/0008976       A1       1/2007       Meenan         2007/00118596       A1 * 5/2007       Patiejunas       709/203         2007/021633       A1 * 9/2007       Gunawardena et al.       370/232         2007/0255861       A1       11/2007       Kain et al.       370/232         2008/0046891       A1       5/2008       Sanchorawala et al.       2009/015829       A1 * 5/2008       Furukawa       718/102         2009/0158299       A1 * 6/2009       Carter       719/319       709/                                                                                                                                   | 7,770,179    | B1   | 8/2010  | James-Roxby et al.        |

| 8,132,001         B1         3/2012         Patten et al.         709/235           2002/0007420         A1*         1/2002         Eydelman et al.         709/235           2002/0167965         A1*         1/2002         Beasley et al.         370/465           2003/0084190         A1         5/2003         Kimball           2004/0049624         A1         3/2004         Salmonsen           2004/020320         A1         5/2004         Lee et al.           2004/0210320         A1         10/2004         Peikari           2006/0026162         A1         2/2006         Salmonsen et al.           2006/0133370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/018596         A1*         5/2007         Patiejunas         709/203           2007/021633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/0046891         A1         2/2008         Sanchorawala et al.         5/2008           2009/0158299         A1*         6/2009         Carter         719/319                                                                                                            | 7,886,340    | B2   | 2/2011  | Carley                    |

| 2002/0007420         A1*         1/2002         Eydelman et al.         709/235           2002/0167965         A1*         11/2002         Beasley et al.         370/465           2003/0084190         A1         5/2003         Kimball           2004/0049624         A1         3/2004         Salmonsen           2004/0143751         A1         7/2004         Lee et al.           2004/0210320         A1         10/2004         Pandya           2006/0026162         A1         2/2006         Salmonsen et al.           2006/0133370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/0118596         A1*         5/2007         Patiejunas         709/203           2007/0211633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.         2008/046891         A1         2/2008           2008/019665         A1         5/2008         Sunchorawala et al.         2009/01235263         A1*         1/2009           2009/01235263         A1*         1/2010         Kuroda et al.         718/102           2010/0005323 <t< td=""><td>8,055,822</td><td>B2 *</td><td>11/2011</td><td>Bernstein et al 710/65</td></t<> | 8,055,822    | B2 * | 11/2011 | Bernstein et al 710/65    |

| 2002/0167965         A1*         11/2002         Beasley et al.         370/465           2003/0084190         A1         5/2003         Kimball         370/465           2004/0049624         A1         3/2004         Salmonsen           2004/0143751         A1         7/2004         Peikari           2004/0210320         A1         10/2004         Pandya           2006/0026162         A1         2/2006         Salmonsen et al.           2007/0008976         A1         1/2007         Meenan           2007/00118596         A1*         5/2007         Patiejunas         709/203           2007/0211633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/046891         A1         2/2008         Sanchorawala et al.         2008/0046891         A1         5/2008         Kuhlmann et al.           2009/0126003         A1         5/2009         Touboul         719/319           2009/01258299         A1*         6/2009         Carter         719/319           2010/00131729         A1         1/2010         Kuroda et al.         713/300           2010                                                                                        | 8,132,001    | B1   | 3/2012  | Patten et al.             |

| 2003/0084190         A1         5/2003         Kimball           2004/0049624         A1         3/2004         Salmonsen           2004/0093520         A1         5/2004         Lee et al.           2004/0210320         A1         10/2004         Peikari           2006/0026162         A1         2/2006         Salmonsen et al.           2006/0133370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/00118596         A1*         1/2007         Meenan           2007/0211633         A1*         9/2007         Gunawardena et al.         370/232           2007/0215861         A1         1/2007         Kain et al.         370/232           2008/0046891         A1         2/2008         Sanchorawala et al.           2008/0126003         A1         5/2008         Kuhlmann et al.           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         1/2010         Kuroda et al.         718/102           2010/0131729         A1         5/2010         Asnaashari         709/230           2010/013579         A1*         7/2010                                                                                                             | 2002/0007420 | A1*  | 1/2002  |                           |

| 2004/0049624         A1         3/2004         Salmonsen           2004/0093520         A1         5/2004         Lee et al.           2004/0143751         A1         7/2004         Peikari           2004/0210320         A1         10/2004         Pandya           2006/0026162         A1         2/2006         Salmonsen et al.           2006/0133370         A1         6/2006         Eldar           2007/008976         A1         1/2007         Meenan           2007/0218596         A1*         5/2007         Patiejunas         709/203           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/0046891         A1         2/2008         Sanchorawala et al.         Sanchorawala et al.           2009/0126003         A1         5/2008         Kuhlmann et al.           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0131729         A1         5/2010         Kuroda et al.         713/300           2010/0135719         A1*         7/2010         Kansashari         709/230           2010/01385719 </td <td>2002/0167965</td> <td>A1*</td> <td>11/2002</td> <td>Beasley et al 370/465</td>          | 2002/0167965 | A1*  | 11/2002 | Beasley et al 370/465     |

| 2004/0093520         A1         5/2004         Lee et al.           2004/0143751         A1         7/2004         Peikari           2004/0210320         A1         10/2004         Peikari           2006/0026162         A1         1/2006         Salmonsen et al.           2006/0133370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/0118596         A1*         5/2007         Patiejunas         709/203           2007/021633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/0046891         A1         2/2008         Sanchorawala et al.         5/2008           2009/0126003         A1         5/2008         Kuhlmann et al.         5/2009           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0131729         A1         5/2010         Kuroda et al.         713/300           2010/0138719         A1*         7/2010         Howard         709/230                                                                                                 | 2003/0084190 | A1   | 5/2003  | Kimball                   |

| 2004/0143751         A1         7/2004         Peikari           2004/0210320         A1         10/2004         Pandya           2006/0026162         A1         2/2006         Salmonsen et al.           2006/0133370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/0218596         A1*         5/2007         Patiejunas         709/203           2007/0211633         A1*         5/2007         Patiejunas         709/203           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/01665         A1         5/2008         Sanchorawala et al.         2008/019665         A1         5/2008           2009/0126003         A1         5/2009         Touboul         719/319           2009/0125829         A1*         6/2009         Carter         719/319           2010/0005323         A1*         1/2010         Kuroda et al.         713/300           2010/0115116         A1*         5/2010         Asnaashari         709/233           2010/0185719         A1*         7/2010         Howard         709/201           2011/0002184         A1         1/2011 </td <td>2004/0049624</td> <td>A1</td> <td>3/2004</td> <td>Salmonsen</td>                         | 2004/0049624 | A1   | 3/2004  | Salmonsen                 |

| 2004/0210320         A1         10/2004         Pandya           2006/0026162         A1         2/2006         Salmonsen et al.           2006/0033370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/002421         A1         1/2007         Lescouet et al.           2007/0211633         A1*         5/2007         Patiejunas         709/203           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/0046891         A1         2/2008         Sanchorawala et al.         2008/0046891         5/2009         Sanchorawala et al.           2009/0126003         A1         5/2009         Touboul         719/319           2009/0158299         A1*         6/2009         Carter         719/319           2010/0005323         A1*         1/2010         Kuroda et al.         718/102           2010/0131729         A1         5/2010         Asnaashari         709/230           2010/0138719         A1*         7/2010         Howard         709/201           2011/0019225         A1         7/2010         Ma et al.           2011/007357         A1         4/2011 <td>2004/0093520</td> <td>A1</td> <td>5/2004</td> <td>Lee et al.</td>                      | 2004/0093520 | A1   | 5/2004  | Lee et al.                |

| 2006/0026162         A1         2/2006         Salmonsen et al.           2006/0133370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/0022421         A1         1/2007         Lescouet et al.           2007/0118596         A1*         5/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/0046891         A1         2/2008         Sanchorawala et al.         2008/019665           2009/0126003         A1         5/2009         Kuhlmann et al.         5/2009           2009/0128299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         1/2010         Kuroda et al.         718/102           2010/0005323         A1*         1/2010         Kuroda et al.         709/230           2010/0131729         A1         5/2010         Asnasahari         709/230           2010/0138719         A1*         7/2010         Howard         709/201           2011/0088037         A1         1/2011         Kim           2011/0107357         A1         5/2011         Glist                                                                                        | 2004/0143751 | A1   | 7/2004  | Peikari                   |

| 2006/0133370         A1         6/2006         Eldar           2007/0008976         A1         1/2007         Meenan           2007/0018596         A1 * 5/2007         Patiejunas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2004/0210320 | A1   | 10/2004 | Pandya                    |

| 2007/0008976         A1         1/2007         Meenan           2007/0022421         A1         1/2007         Lescouet et al.           2007/0118596         A1*         5/2007         Patiejunas         709/203           2007/0211633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.           2008/0109665         A1         5/2008         Sanchorawala et al.           2009/0126003         A1         5/2009         Touboul           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0005323         A1*         1/2010         Kuroda et al.         713/300           2010/0115116         A1*         5/2010         Fulcheri et al.         709/230           2010/0185719         A1*         7/2010         Howard         709/201           2011/00192225         A1         7/2010         Ma et al.           2011/0088037         A1         4/2011         Glistvain           2011/0107357         A1         5/2011         Cullimore           2012/0017262<                                                                                                | 2006/0026162 | A1   | 2/2006  | Salmonsen et al.          |

| 2007/0022421         A1         1/2007         Lescouet et al.           2007/0118596         A1*         5/2007         Patiejunas         709/203           2007/0211633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.         2008/0046891         A1         2/2008         Sanchorawala et al.         2008/0126003         A1         5/2009         Touboul         719/319           2009/0126003         A1         5/2009         Touboul         718/102           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0005323         A1*         1/2010         Kuroda et al.         713/300           2010/0115116         A1*         5/2010         Asnaashari         709/230           2010/0131729         A1         5/2010         Fulcheri et al.           2010/0192255         A1         7/2010         Ma et al.         709/201           2011/002184         A1         1/2011         Kim         1/2011         Kim           2011/0107357         A1         5/2011         Glistvain         2011/0107357         A1         5/2011         Cullimore           20                                                                        |              |      |         |                           |

| 2007/0118596         A1*         5/2007         Patiejunas         709/203           2007/0211633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.           2008/0046891         A1         2/2008         Sanchorawala et al.           2009/0126003         A1         5/2008         Kuhlmann et al.           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0005323         A1*         1/2010         Kuroda et al.         709/230           2010/0131729         A1         5/2010         Asnaashari         709/230           2010/0185719         A1*         7/2010         Howard         709/201           2011/00192225         A1         1/2011         Kim           2011/0088037         A1         4/2011         Glistvain           2011/0107357         A1         5/2011         Cullimore           2012/0017262         A1         1/2012         Kapoor et al.                                                                                                                                                                                              |              | A1   |         | Meenan                    |

| 2007/0211633         A1*         9/2007         Gunawardena et al.         370/232           2007/0255861         A1         11/2007         Kain et al.         370/232           2008/0046891         A1         2/2008         Sanchorawala et al.         5           2008/0126003         A1         5/2009         Kuhlmann et al.         719/319           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0005323         A1*         1/2010         Kuroda et al.         719/330           2010/0131729         A1         5/2010         Asnaashari         709/230           2010/0185719         A1*         7/2010         Howard         709/201           2011/00192225         A1         7/2010         Ma et al.         709/201           2011/0088037         A1         4/2011         Glistvain           2011/0107357         A1         5/2011         Cullimore           2012/0017262         A1         1/2012         Kapoor et al.                                                                                                                                                                                                                   | 2007/0022421 |      | 1/2007  |                           |

| 2007/0255861       A1       11/2007       Kain et al.         2008/0046891       A1       2/2008       Sanchorawala et al.         2008/0109665       A1       5/2008       Kuhlmann et al.         2009/0126003       A1       5/2009       Touboul         2009/0235263       A1*       9/2009       Furukawa       718/102         2010/0005323       A1*       1/2010       Kuroda et al.       713/300         2010/0131729       A1       5/2010       Kanaashari       709/230         2010/0185719       A1*       7/2010       Fulcheri et al.       709/201         2011/0002184       A1       1/2011       Kim       709/201         2011/0107357       A1       5/2011       Glistvain         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2007/0118596 | A1*  | 5/2007  |                           |

| 2008/0046891       A1       2/2008       Sanchorawala et al.         2008/0109665       A1       5/2009       Kuhlmann et al.         2009/0126003       A1       5/2009       Touboul         2009/0158299       A1*       6/2009       Carter       719/319         2009/0235263       A1*       9/2009       Furukawa       718/102         2010/0005323       A1*       1/2010       Kuroda et al.       713/300         2010/0115116       A1*       5/2010       Asnaashari       709/230         2010/0131729       A1       5/2010       Fulcheri et al.         2010/0185719       A1*       7/2010       Howard       709/201         2011/00192225       A1       7/2010       Ma et al.         2011/0088037       A1       1/2011       Kim         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                           | 2007/0211633 | A1*  | 9/2007  | Gunawardena et al 370/232 |

| 2008/0109665         A1         5/2008         Kuhlmann et al.           2009/0126003         A1         5/2009         Touboul           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0005323         A1*         1/2010         Kuroda et al.         713/300           2010/0115116         A1*         5/2010         Asnaashari         709/230           2010/0131729         A1         5/2010         Fulcheri et al.           2010/0185719         A1*         7/2010         Howard         709/201           2011/00192225         A1         7/2010         Ma et al.         1/2011           2011/002184         A1         1/2011         Kim         1/2011           2011/0107357         A1         5/2011         Glistvain           2011/0107262         A1         1/2012         Kapoor et al.                                                                                                                                                                                                                                                                                                                                                           | 2007/0255861 |      | 11/2007 | Kain et al.               |

| 2009/0126003         A1         5/2009         Touboul           2009/0158299         A1*         6/2009         Carter         719/319           2009/0235263         A1*         9/2009         Furukawa         718/102           2010/0005323         A1*         1/2010         Kuroda et al.         713/300           2010/0115116         A1*         5/2010         Asnaashari         709/230           2010/0185719         A1*         7/2010         Howard         709/201           2010/0192225         A1         7/2010         Ma et al.         1/2011           2011/0002184         A1         1/2011         Kim         1/2011           2011/0107357         A1         5/2011         Glistvain           2011/017262         A1         1/2012         Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2008/0046891 | A1   |         |                           |

| 2009/0158299     A1*     6/2009     Carter     719/319       2009/0235263     A1*     9/2009     Furukawa     718/102       2010/0005323     A1*     1/2010     Kuroda et al.     713/300       2010/0115116     A1*     5/2010     Asnaashari     709/230       2010/0131729     A1     5/2010     Fulcheri et al.       2010/0185719     A1*     7/2010     Howard     709/201       2010/0192225     A1     7/2010     Ma et al.       2011/0002184     A1     1/2011     Kim       2011/0107357     A1     5/2011     Glistvain       2011/0107262     A1     1/2012     Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2008/0109665 | A1   | 5/2008  | Kuhlmann et al.           |

| 2009/0235263       A1*       9/2009       Furukawa       718/102         2010/0005323       A1*       1/2010       Kuroda et al.       713/300         2010/0115116       A1*       5/2010       Asnaashari       709/230         2010/0131729       A1       5/2010       Fulcheri et al.       709/201         2010/0185719       A1*       7/2010       Howard       709/201         2010/0192225       A1       7/2010       Ma et al.         2011/0002184       A1       1/2011       Kim         2011/0088037       A1       4/2011       Glistvain         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |      |         |                           |

| 2010/0005323       A1*       1/2010       Kuroda et al.       713/300         2010/0115116       A1*       5/2010       Asnaashari       709/230         2010/0131729       A1       5/2010       Fulcheri et al.       709/201         2010/0185719       A1*       7/2010       Howard       709/201         2010/0192225       A1       7/2010       Ma et al.         2011/0002184       A1       1/2011       Kim         2011/0088037       A1       4/2011       Glistvain         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |      |         |                           |

| 2010/0115116       A1*       5/2010       Asnaashari       709/230         2010/0131729       A1       5/2010       Fulcheri et al.       709/201         2010/0185719       A1*       7/2010       Howard       709/201         2010/0192225       A1       7/2010       Ma et al.         2011/0088037       A1       1/2011       Kim         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |      |         |                           |

| 2010/0131729       A1       5/2010       Fulcheri et al.         2010/0185719       A1*       7/2010       Howard       709/201         2010/0192225       A1       7/2010       Ma et al.         2011/0002184       A1       1/2011       Kim         2011/0088037       A1       4/2011       Glistvain         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |      |         |                           |

| 2010/0185719       A1*       7/2010       Howard       709/201         2010/0192225       A1       7/2010       Ma et al.         2011/0002184       A1       1/2011       Kim         2011/0107357       A1       4/2011       Glistvain         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | A1*  |         |                           |

| 2010/0192225       A1       7/2010       Ma et al.         2011/0002184       A1       1/2011       Kim         2011/0088037       A1       4/2011       Glistvain         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |      |         |                           |

| 2011/0002184       A1       1/2011       Kim         2011/0088037       A1       4/2011       Glistvain         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |      |         |                           |

| 2011/0088037       A1       4/2011       Glistvain         2011/0107357       A1       5/2011       Cullimore         2012/0017262       A1       1/2012       Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |      |         |                           |

| 2011/0107357 A1 5/2011 Cullimore<br>2012/0017262 A1 1/2012 Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |      |         |                           |

| 2012/0017262 A1 1/2012 Kapoor et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |      |         |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |      |         |                           |

| 2012/0042088 A1 2/2012 Cullimore                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |      |         |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2012/0042088 | Al   | 2/2012  | Cullimore                 |

#### OTHER PUBLICATIONS

Bathen et al. "Inter and Intra Kernel Reuse Analysis Driven Pipelining on Chip-Multiprocessors," International Symposium on VLSI Design, Automation and Test, Apr. 26-29, 2010. p. 203-207. [Accessed Feb. 16, 2011—IEEExplore] http://ieeexplore.ieee.org/xpis/abs all.jsp?amumber=5496725.

Bolchini et al. "Smart Card Embedded Information Systems: A Methodology for Privacy Oriented Architectural Design," Data & Knowledge Engineering, 2002. vol. 41, No. 2-3, p. 159-182. [Accessed Feb. 16, 2011-ScienceDirect.com].

Ferrante et al. "Application-Driven Optimization of VLIW Architectures: A Hardware—Software Approach," 11th IEEE Real Time and Embedded Technology and Applications Symposium, Mar. 7-10, 2005. pp. 128-137. [Accessed Feb. 15, 2011-IEEExplore] http://ieeexplore.ieee.org/xpls/abs\_all.jsp?arnumber=1388380.

Green Hills Software, "1-I-velOSityTM Real-Time Microkemel," Accessed on Feb. 16, 2011 at http://www.ghs.com/products/micro\_velosity.html.

Green Hills Software, Inc., "μ-velOSity Microkernel," (datasheet)

Hattori. "Challenges for Low-Power Embedded SOC's," International Symposium on VLSI Design, Automation and Test, Apr. 25-27, 2007. p. 1. [Accessed Feb. 16, 2011—IEEExplore] http://ieeexplore.ieee.org/xpis/abs\_all.jsp?arnumber=4239406.

Journal of Techonology & Science, "Express Logic, Inc.; Express Logic and IAR Systems Team Up to Provide ThreadX RTOS Support in IAR Embedded Workbench IDE for Freescale ColdFire," Accessed on Feb. 16, 2011 at http://proquest.umi.com.mutex.gmu.edu/pqdweb?index=7 & did=1541305....

Ke et al. "Design of PC/1 04 Processor Module Based on ARM," International Conference on Electrical and Control Engineering, Jun. 25-27, 2010. p. 775-777. [Accessed Feb. 17, 2011—IEEExplore] http://ieeexplore.ieee.org/xpis/abs\_all.jsp?arnumber=5630566.

Kinebuchi et al. "A Hardware Abstraction Layer for Integrating Real-Time and General-Purpose with Minimal Kernel Modification," Software Technologies for Future Dependable Distributed Systems, Mar. 17, 2009. p. 112-116.[Accessed Feb. 16, 2011-IEEExplore] http:// ieeexplore.ieee.org/xpls/abs\_all.jsp?arnumber=4804582.

Tabari, et al. "Neural Network Processor for a FPGA-based Multiband Fluorometer Device," International Workshop on Computer Architecture for Machine Perception and Sensing, Aug. 18-20, 2006. p. 198-202. [Accessed Feb. 16, 2011—IEEExplore] http://ieeexplore.ieee.org/xpls/abs\_all.jsp?amumber=4350381.

Wang et al. "Towards High-Performance Network Intrusion Prevention System on Multi-core Network Services Processor," 15th International Conference on Parallel and Distributed Systems, Dec. 8-11, 2009. p. 220-227. [Accessed Feb. 16, 2011—IEEExplore].

Nguyen et al. "Real-Time Operating Systems for Small Microcontrollers," IEEE Micro, Sep.-Oct. 2009. vol. 29, No. 5, p. 30-45. [Accessed Feb. 15, 2011—IEEExplore] http://ieeexplore.ieee.org/xpis/abs\_all.jsp?arnumber=5325154.

Ashkenazi et al. "Platform Independent Overall Security Architecture in Multi-Processor System-on-Chip ICs for Use in Mobile Phones and Handheld Devices," World Automation Congress, Jul. 24-26, 2006. [Accessed Feb. 18, 2011—Engineering Village].

Bathen et al. "Inter and Intra Kernel Reuse Analysis Driven Pipelining on Chip—Multiprocessors," International Symposium on VLSI Design, Automation and Test, Apr. 26-29, 2010. p. 203-206. [Accessed Feb. 16, 2011—IEEExplore] http://ieeexplore.ieee.org/xpis/abs all.jsp?amumber=5496725.

Bolchini et al. "Smart Card Embedded Information Systems: A Methodology for Privacy Oriented Architectural Design," Data & Knowledge Engineering, 2002. vol. 41, p. 159-182. [Accessed Feb. 16, 2011—ScienceDirect.com].

Cavium Networks, "Nitrox® DPI L7 Content Processor Family," Accessed on Feb. 16, 2011 at http://www.caviumnetworks.com/processor\_NITROX-DPI.html.

Cavium Networks, "Nitrox® Lite," Accessed on Feb. 16, 2011 at http://www.caviumnetworks.com/processor\_securitLnitroxLite.

Ferrante et al. "Application-Driven Optimization of VLIW Architectures: A Hardware-Software Approach," Proceedings of the 11th IEEE Real Time and Embedded Technology and Applications Symposium, Mar. 7-10, 2005. p. 128-137. [Accessed Feb. 15, 2011—IEEExplore] http://ieeexplore.ieee.org/xpls/abs\_all.jsp?arnumber=1388380.

Freescale Semiconductor, "IP Multimedia Subsystems," 2006. (brochure) [Accessed Feb. 16, 2011] http://cacheJreescale.com/files/32biUdoc/brochure/BRIMSSOLUTIONS.pdf.

Green Hills Software, "µ-velOSity Real-Time Microkernel," Accessed on Feb. 16, 2011 at http://www.ghs.com/products/micro\_velosity. html.

Green Hills Software, Inc., "μ-velOSity Microkernel," (datasheet—2pgs.) 2006.

Hattori. "Challenges for Low-Power Embedded SOC's," International Symposium on VLSI Design, Automation and Test, Apr. 25-27, 2007. 4pgs. [Accessed Feb. 16, 2011—IEEExplore] http://ieeexplore.ieee.org/xpis/abs\_all.jsp? arnumber=4239406.

Journal of Technology & Science, "Express Logic, Inc.; Express Logic and IAR Systems Team Up to Provide ThreadX RTOS Support in IAR Embedded Workbench IDE for Freescale ColdFire," Accessed on Feb. 16, 2011 at http://proquest.umi.com.mutex.gmu.edu/pqdweb?index=7 &did=1541305....

Kakarountas et al. "Implementation of HSSec: A High-Speed Cryptographic Co-Processor," IEEE Conference On Emerging Technologies and Factory Automation, Sep. 25-28, 2007. p. 625-631. [Accessed Feb. 16, 2011—IEEExplore] http://ieeexplore.ieee.org/xpls/abs\_all.jsp?amumber=4416827.

Ke et al. "Design of PC/104 Processor Module Based on ARM," International Conference on Electrical and Control Engineering, Jun. 25-27, 2010. p. 775-777. [Accessed Feb. 17, 2011—IEEExplore] http://ieeexplore.ieee.org/xpis/abs\_all.jsp?arnumber=5630566.

#### (56) References Cited

#### OTHER PUBLICATIONS

Kinebuchi et al. "A Hardware Abstraction Layer for Integrating Real-Time and General-Purpose with Minimal Kernel Modification," Software Technologies for Future Dependable Distributed Systems, Mar. 17, 2009. p. 112-116.[Accessed Feb. 16, 2011—IEEExplore] http:// ieeexplore.ieee.org/xpls/abs\_all.jsp?arnumber=4804582.

Tabari, et al. "Neural Network Processor for a FPGA-based Multiband Fluorometer Device," International Workshop on Computer Architecture for Machine Perception and Sensing, Sep. 2006. p. 198-202. [Accessed Feb. 16, 2011—IEEExplore] http://ieeexplore.ieee.org/xpls/abs\_all.jsp?amumber=4350381.

Wang et al. "Towards High-Performance Network Intrusion Prevention System on Multi-core Network Services Processor," 15th International Conference on Parallel and Distributed Systems, Dec. 8-11, 2009. p. 220-227. [Accessed Feb. 16, 2011—IEEExplore].

Wong, William, "16-Bit MCU Invades 8-Bit Territory with 4-by 4-mm Chip," Electronic Design, Sep. 29, 2005. vol. 53, No. 21, p. 32. [Accessed Feb. 16, 2011—Academic Search Complete].

"Yoggie Pico Personal Security Appliance," www.yoggie.com. (archived on May 31, 2009) [Accessed Feb. 16, 2011—Archive.org].

"Yoggie Security Unveils Miniature Hardware Appliance," www. yoggie.com. (archived on May 31, 2009) [Accessed Feb. 16, 2011—Archive.org].

"Yoggie Unveils Miniature Internet Security Devices for Mac Computers," M2 Telecomworldwire,Oct. 14, 2008. [Accessed Feb. 18, 2011—Academic Source Complete].

Quan Huang et al.: "Embedded firewall based on network processor", 2005, IEEE, Proceedings of the Second International Conference on Embedded Software and Systems (ICESS'05), 7 pages.

Tan et al.: "A simulation framework for energy-consumption analysis of OS-driven embedded applications," IEEE, vol. 22, No. 9, Sep. 2003.

International Search Report and Written Opinion mailed Dec. 30, 2010 in Patent Cooperation Treaty application No. PCT/US10/55186, filed Nov. 2, 2010.

Benini et al.: "Finite-state machine partitioning for low power," 1998, IEEE

Antoniou, S. "Networking Basics: TCP, UDP, TCP/IP and OSI Model," Oct. 29, 2007, <a href="www.translingal.com/blog/networking-basics-tco=udp-tcpip-osi-models">www.translingal.com/blog/networking-basics-tco=udp-tcpip-osi-models</a> (retrieved Jun. 4, 2013) 8 pages.

\* cited by examiner

FIG. 1

| 210                      | 210 APPLICATIONS            |                                 |                             |                           |                                      |  |

|--------------------------|-----------------------------|---------------------------------|-----------------------------|---------------------------|--------------------------------------|--|

| 280                      | SOCKETS API                 |                                 |                             |                           |                                      |  |

| TCP<br>EXTENSIONS<br>230 |                             | UDP<br>EXTENSIONS<br><u>234</u> |                             | ICMP<br>EXTENSIONS<br>238 |                                      |  |

| TCP STACK<br>232         |                             | UDP STACK<br>236                |                             | ICMP STACK<br><u>240</u>  |                                      |  |

| 250 IP LAYER             |                             |                                 |                             |                           |                                      |  |

| Device Driver<br>260     | Device Driver<br><u>262</u> |                                 | Device Driver<br><u>264</u> |                           | Ethernet<br>Controller<br><u>270</u> |  |

| 220 HARDWARE             |                             |                                 |                             |                           |                                      |  |

FIG. 3

FIG. 4

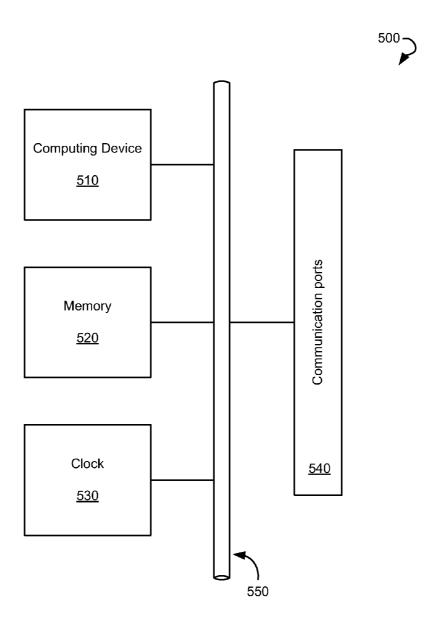

FIG. 5

# MASSIVELY MULTICORE PROCESSOR AND OPERATING SYSTEM TO MANAGE STRANDS IN HARDWARE

## CROSS REFERENCES TO RELATED APPLICATIONS

This application is a continuation of U.S. patent application Ser. No. 13/224,938, filed on Sep. 2, 2011, entitled "Massively Multicore Processor and Operating System to Manage Strands in Hardware," which is incorporated by reference in its entirety. This application is also related to U.S. patent application Ser. No. 13/277,111, filed on Oct. 19, 2011, entitled, "TCP/IP Stack-Based Operating System," which is a continuation of U.S. patent application Ser. No. 12/938,290, filed on Nov. 2, 2010, entitled, "TCP/IP Stack-Based Operating System," both of which are incorporated by reference in their entirety.

#### TECHNICAL FIELD

The application generally relates to computing devices having multiple processors and, more specifically, to a multicore processor and operating system based on a protocol 25 stack.

#### BACKGROUND

Computing devices such as desktop computers, laptop 30 computers, cell phones, smartphones, personal digital assistants (PDA), and many other electronic devices are widely deployed. The primary element of such computing devices is a central processing unit (CPU), or a processor, which is responsible for executing instructions of one or more computer programs. The CPU executes each program instruction in sequence to perform the basic arithmetical, logical, and input/output operations of the computing device. Design and implementation of such devices in general, and CPUs in particular, may vary; however, their fundamental functional-ities remain very similar.

Traditionally, in a computing device, the CPU is coupled to a memory and an Input/Output (I/O) subsystem, directly or through a bus, to perform the main functions of computing 45 devices such as inputting and outputting data, processing data, and so forth. The memory may embed an operating system (OS), computer programs, applications, and so forth.

Conventional operating systems are quite similar in architecture, in that each tends to have conventional file and 50 memory operations, storage and graphical user interface operations, and so forth. Architectures of conventional operating systems include a layered design, device drivers, and Application Programming Interfaces (APIs).

In conventional operating systems, a core kernel essentially has master control over all the operations of the overlying software, components, device drivers, applications, and so forth. Traditionally, operating systems implement 'multitasking' through time slicing and sequential allocation of computer resources to various threads and processes. A 60 thread generally runs within a process and shares resources, e.g., memory, with other threads within the same process, whereas a process generally runs 'self-contained' within its own right and completely independently of any other process. In multi-tasking, when a computing device includes a single 65 processor, the operating system instructs the processor to switch between different threads and implement them

2

sequentially. Switching generally happens frequently enough that the user may perceive the threads (or tasks) as running simultaneously.

Many conventional computing devices utilize multiprocessors, or multicore processors, which may truly allocate multiple threads or tasks to run at the same time on different cores. However, conventional multicore processor architectures involve a small number of cores (typically 2, 4, 6, or 8 cores) due to the design limitations of traditional hardware and traditional operating systems. In the case of a conventional multicore processor, the computing device still must implement time slicing and switching between different threads on each of its cores when performing several tasks involving multithreading allocated through the cores. In other words, even conventional multicore processors cannot implement true multitasking.

Traditional processor architectures are also known to experience hanging, cycling, or crashing of the threads when applications are poorly written or purposely malicious. In many instances, a thread crash may bring the whole processor down and result in time-division multiplexing of various threads or processes.

Conventional processor designs use a fixed-frequency, continuously running crystal as the timing mechanism for clocking through microprocessor execution cycles. Thus, the crystal and the processor may continue running even if nothing is being accomplished in the computing device, uselessly cycling around and waiting for a process to actually perform an action. This timing paradigm results in wasted energy. First, the crystal and processor transistors typically execute at their maximum speed at all times, thereby consuming excess power and generating excess heat. Secondly, it is inefficient to continue running clock cycles if no substantive process is actually running. However, these inefficiencies are unavoidable in the conventional operating system design.

Furthermore, conventional operating systems require various modifications and enhancements each year, such as incorporation of new communications layers for Ethernet drivers, Transmission Control Protocol/Internet Protocol (TCP/IP) stacks, Web browsers, and the like. Generally, these new layers are added on top of the conventional operating system, thereby increasing complexity, decreasing performance, and often leading to software crashes and security flaws.

#### **SUMMARY**

This summary is provided to introduce a selection of concepts in a simplified form that are further described below in the Detailed Description. This summary is not intended to identify key features or essential features of the claimed subject matter, nor is it intended to be used as an aid in determining the scope of the claimed subject matter.

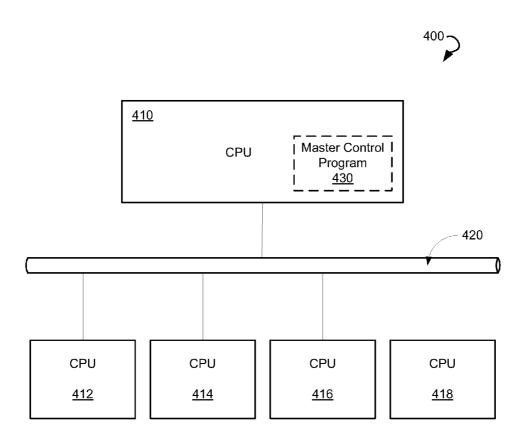

In accordance with various embodiments disclosed herein, a computing device having multiple CPUs interconnected to each other is provided. Each CPU embeds an operating system of an entirely new architecture. This operating system may be based fundamentally around an Internet stack, for example, the TCP/IP stack (instead of including a TCP/IP layer as in a conventional core operating system) and may utilize a conventional interface or similar extensions of the standard Berkeley Sockets (or WinSock) APIs.

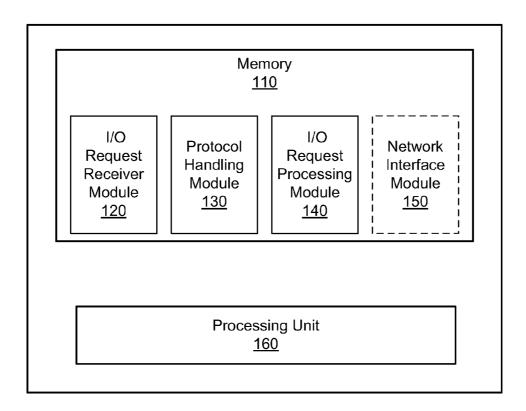

In accordance with various embodiments disclosed herein, a computing apparatus is provided. The computing apparatus may comprise a set of interconnected central processing units. Each CPU may embed an operating system (OS) comprising an operating system kernel, the operating system kernel being a state machine and comprising a protocol stack. At

least one of the CPUs may further embed executable instructions for allocating multiple strands to one or more other CPUs of the set of interconnected CPUs. It will be understood that a strand, as used herein, is a hardware oriented process and is not necessarily similar to a conventional unit of processing (i.e., a thread) that can be scheduled by an operating system. The Internet stack is a set of communication protocols used for the Internet and other similar networks. In one example embodiment, the Internet stack may comprise a TCP/IP stack such that the OS kernel is a TCP/IP stack state machine with proprietary extensions that can be used to change or access internals of the TCP/IP stack state machine. In another example embodiment, the Internet stack may comprise a User Datagram Protocol/Internet Protocol (UDP/IP) stack such that the OS kernel is a UDP/IP stack state machine 15 with proprietary extensions that can be used to change or access internals of the UDP/IP stack state machine. The CPU may comprise a processing unit, a memory and an I/O interface. Executable instructions for the operating system may be stored within one or more types of storage media, such as for 20 example, Read-Only Memory (ROM), Programmable Read-Only Memory (PROM), Field Programmable Read-Only Memory (FPROM), One-Time Programmable Read-Only Memory (OTPROM), One-Time Programmable Non-Volatile Memory (OTP NVM), Erasable Programmable Read- 25 according to an exemplary embodiment. Only Memory (EPROM), and Electrically Erasable Programmable Read-Only Memory (EEPROM or Flash ROM).

The computing apparatus may further comprise at least one asynchronous clock to serve as an internal clock for the operating system. The asynchronous clock may be configurable to 30 automatically stop when clock cycles are no longer needed. A time reference for the operating system kernel may be based, for example, on a Network Time Protocol (NTP), Simple Network Time Protocol (SNTP), or other suitable time protocol from a remote time server. In an example, the operating 35 system may utilize a Sockets style API of sockets and ports on IP addresses for handling I/O requests. The set of CPUs may be interconnected through a bus. Executable instructions for the operating system may be executed through a Sockets API. allocating multiple strands may further comprise instructions for generating multiple strands.

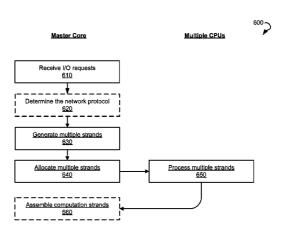

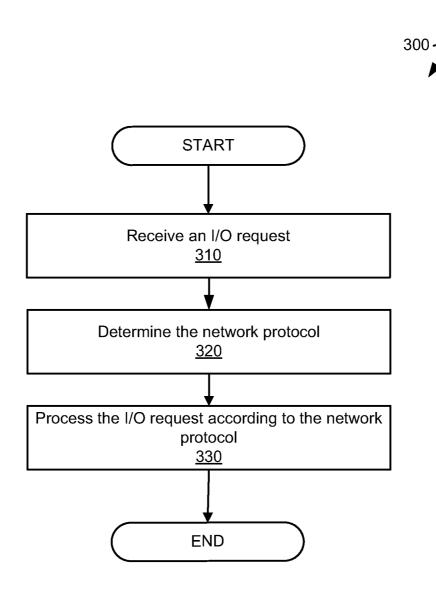

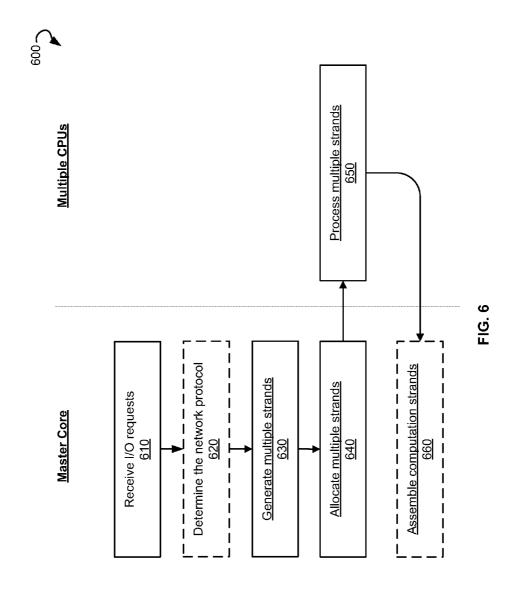

According to another embodiment, a method for operating a computing apparatus is provided. The method may comprise receiving I/O requests, generating multiple strands 45 according to the I/O requests, allocating the multiple strands to one or more CPUs of a set of CPUs, and processing the multiple strands. Each CPU may embed an operating system (OS) having a kernel comprising a protocol stack.

According to various embodiments, the I/O requests may 50 be received by a CPU, which embeds executable instructions for allocating multiple strands through multiple CPUs. Allocating multiple strands may comprise communicating data via a network interface.

In one embodiment, the method may further comprise 55 assembling results of multiple strands processing. Executable instructions for the operating system may be stored in a memory and executed through a Sockets API.

According to some embodiments, a non-transitory computer-readable storage medium is provided having embodied 60 instructions thereon, instructions executable by a processor in a computing device to perform a method. The method may comprise receiving an input/output (I/O) request, generating one or more strands according to the I/O request, allocating the one or more strands and/or processes to one or more 65 central processing units (CPUs) of a set of CPUs, wherein each CPU of the set embeds an operating system (OS) having